I have an issue about the PCI Pool selector.

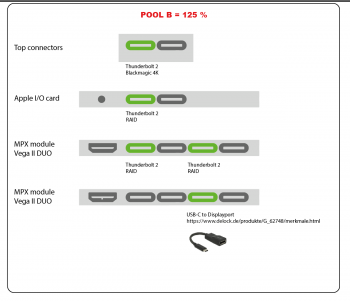

I have two Vega II DUO, so 4 BUS on them and 1 BUS with Mac I/O and 1 BUS at the top of the Mac. So 6 Thunderbolt BUS in total.

I have 3 RAID HDD tower (all of them are Thunderbolt 2) and a Blackmagic 4 k extreme (connected by Thunderbolt 2), + 2k monitor (connected in Display port with an Thunderbolt->Display Port adapter.)

If I connect my material as mentioned bellow. Pool B goes up to 150%... and POOL A stays at 0%, but I don't understand why.

- Vega II Duo Number 1 BUS 0 : RAID tower Number 1

- Vega II Duo Number 1 BUS 1 : RAID tower Number 2

- Vega II Duo Number 2 BUS 0 : RAID tower Number 3

- Vega II Duo Number 2 BUS 1 : Monitor 2k

- Mac I/O : Blackmagic 4k extrem

As I understand, everything should be right... but my POOL B exceed 100% and I can't force the Mac Pro to use POOL A... Do you know why ? Are Thunderbolt material automatically assigned to POOL B ?

I made an other test. If I connect my material as mentioned bellow. Pool B don't exceed 100%... and POOL A stays at 0%.

- Vega II Duo Number 1 BUS 0 : monitor 2k

- Vega II Duo Number 2 BUS 0 : RAID tower Number 1

- Mac I/O : RAID tower Number 2

- Mac I/O : RAID tower Number 3

- Top Thunderbolt PORT : Blackmagic 4k extrem

For me it's not normal. And more strange, if I disconnect everything PCI indicator tells me that PCI cards aren't arranged in optimal configuration. (But this configuration comes from APPLE, two MPX and Mac I/O card).

Maybe, I'm wrong on something, but I don't know about what. I found a good article about this subject here : https://softron.zendesk.com/hc/en-u...OW-TO-Install-PCIe-cards-in-your-2019-Mac-Pro

Best

Robin

I have two Vega II DUO, so 4 BUS on them and 1 BUS with Mac I/O and 1 BUS at the top of the Mac. So 6 Thunderbolt BUS in total.

I have 3 RAID HDD tower (all of them are Thunderbolt 2) and a Blackmagic 4 k extreme (connected by Thunderbolt 2), + 2k monitor (connected in Display port with an Thunderbolt->Display Port adapter.)

If I connect my material as mentioned bellow. Pool B goes up to 150%... and POOL A stays at 0%, but I don't understand why.

- Vega II Duo Number 1 BUS 0 : RAID tower Number 1

- Vega II Duo Number 1 BUS 1 : RAID tower Number 2

- Vega II Duo Number 2 BUS 0 : RAID tower Number 3

- Vega II Duo Number 2 BUS 1 : Monitor 2k

- Mac I/O : Blackmagic 4k extrem

As I understand, everything should be right... but my POOL B exceed 100% and I can't force the Mac Pro to use POOL A... Do you know why ? Are Thunderbolt material automatically assigned to POOL B ?

I made an other test. If I connect my material as mentioned bellow. Pool B don't exceed 100%... and POOL A stays at 0%.

- Vega II Duo Number 1 BUS 0 : monitor 2k

- Vega II Duo Number 2 BUS 0 : RAID tower Number 1

- Mac I/O : RAID tower Number 2

- Mac I/O : RAID tower Number 3

- Top Thunderbolt PORT : Blackmagic 4k extrem

For me it's not normal. And more strange, if I disconnect everything PCI indicator tells me that PCI cards aren't arranged in optimal configuration. (But this configuration comes from APPLE, two MPX and Mac I/O card).

Maybe, I'm wrong on something, but I don't know about what. I found a good article about this subject here : https://softron.zendesk.com/hc/en-u...OW-TO-Install-PCIe-cards-in-your-2019-Mac-Pro

Best

Robin