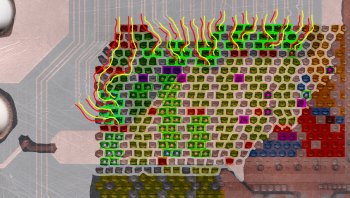

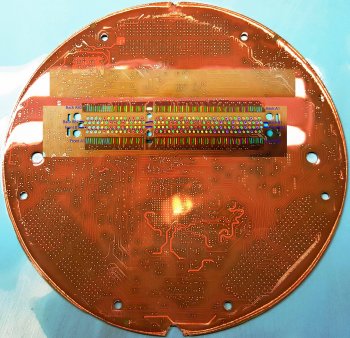

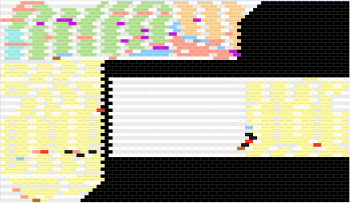

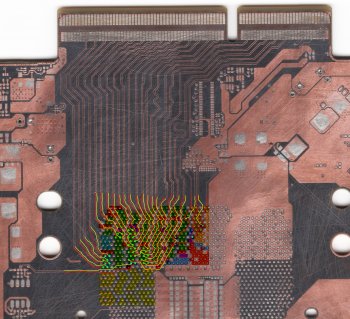

I've mapped all the non-ground non-power pins for the front first layer of the CPU Riser Card. The text isn't quite legible but it is easy enough to correlate it with the color-coded spreadsheet or the portion of it I used for the mapping (I'll include that here as well). Who knew connect-the-dots, 'staying in the lines', using a line to traverse a maze, would come in so handy later in life!

I've confirmed there are 16 PCIe 3.0 transmit pairs and 4 PCIe 2.0 transmit pairs mapped on this layer.

top layer front side of board. I've circled the 47 pads in the spreadsheet. I guess I will list them here too for completeness. The PCIe 3.0 transmit pairs are in bold.

C45|DMI_TX_DP[3]|PCIEX|O

E45|DMI_TX_DN[3]|PCIEX|O

B44|DMI_TX_DP[2]|PCIEX|O

D44|DMI_TX_DN[2]|PCIEX|O

C43|DMI_TX_DP[1]|PCIEX|O

E43|DMI_TX_DN[1]|PCIEX|O

B42|DMI_TX_DP[0]|PCIEX|O

D42|DMI_TX_DN[0]|PCIEX|O

J51|PE3A_TX_DP[1]|PCIEX3|O;2B74

L51|PE3A_TX_DN[1]|PCIEX3|O;2B75

H50|PE3A_TX_DP[0]|PCIEX3|O;2B78

K50|PE3A_TX_DN[0]|PCIEX3|O;2B79

P52|PE3B_TX_DP[4]|PCIEX3|O;2B62

T52|PE3B_TX_DN[4]|PCIEX3|O;2B63

R51|PE3B_TX_DP[5]|PCIEX3|O;2B58

U51|PE3B_TX_DN[5]|PCIEX3|O;2B59

P50|PE3B_TX_DP[6]|PCIEX3|O;2B54

T50|PE3B_TX_DN[6]|PCIEX3|O;2B55

R49|PE3B_TX_DP[7]|PCIEX3|O;2B50

U49|PE3B_TX_DN[7]|PCIEX3|O;2B51

P48|PE3A_TX_DP[3]|PCIEX3|O;2B66

T48|PE3A_TX_DN[3]|PCIEX3|O;2B67

R47|PE3A_TX_DP[2]|PCIEX3|O;2B70

U47|PE3A_TX_DN[2]|PCIEX3|O;2B71

P46|PE3C_TX_DP[8]|PCIEX3|O;2B45

T46|PE3C_TX_DN[8]|PCIEX3|O;2B46

R45|PE3C_TX_DP[10]|PCIEX3|O;2B37

U45|PE3C_TX_DN[10]|PCIEX3|O;2B38

P44|PE3D_TX_DN[15]|PCIEX3|O;2B14

T44|PE3D_TX_DP[15]|PCIEX3|O;2B15

R43|DDR_SDA_C23|ODCMOS|I/O

U43|DDR_SCL_C23|ODCMOS|I/O

AA47|PE3C_TX_DP[9]|PCIEX3|O;2B41

AC47|PE3C_TX_DN[9]|PCIEX3|O;2B42

Y46|PE3C_TX_DP[11]|PCIEX3|O;2B33

AB46|PE3C_TX_DN[11]|PCIEX3|O;2B34

AA45|PE3D_TX_DP[12]|PCIEX3|O;2B27

AC45|PE3D_TX_DN[12]|PCIEX3|O;2B28

Y44|PE3D_TX_DP[13]|PCIEX3|O;2B23

AB44|PE3D_TX_DN[13]|PCIEX3|O;2B24

AA43|PE3D_TX_DN[14]|PCIEX3|O;2B19

AC43|PE3D_TX_DP[14]|PCIEX3|O;2B20

AT50|FRMAGENT|CMOS|I

AT48|BIST_ENABLE|CMOS|I

BA55|TEST4||I

BD50|ERROR_N[0]|ODCMOS|O

BJ53|PWRGOOD|CMOS|I

Update (added pins from the other 3/4 of the CPU):

AE27|DDR_RESET_C23_N|CMOS1.5v|O

D4|TEST3||O

F2|TEST2||O

CB18|DDR_RESET_C01_N|CMOS1.5v|O

CW17|DRAM_PWR_OK_C01|CMOS1.5v|I

DB4|TEST0||O

CW1|TEST1||O

full-size

https://www.dropbox.com/s/kjoo7grsaqb8azm/top01.png?dl=0

I've confirmed there are 16 PCIe 3.0 transmit pairs and 4 PCIe 2.0 transmit pairs mapped on this layer.

top layer front side of board. I've circled the 47 pads in the spreadsheet. I guess I will list them here too for completeness. The PCIe 3.0 transmit pairs are in bold.

C45|DMI_TX_DP[3]|PCIEX|O

E45|DMI_TX_DN[3]|PCIEX|O

B44|DMI_TX_DP[2]|PCIEX|O

D44|DMI_TX_DN[2]|PCIEX|O

C43|DMI_TX_DP[1]|PCIEX|O

E43|DMI_TX_DN[1]|PCIEX|O

B42|DMI_TX_DP[0]|PCIEX|O

D42|DMI_TX_DN[0]|PCIEX|O

J51|PE3A_TX_DP[1]|PCIEX3|O;2B74

L51|PE3A_TX_DN[1]|PCIEX3|O;2B75

H50|PE3A_TX_DP[0]|PCIEX3|O;2B78

K50|PE3A_TX_DN[0]|PCIEX3|O;2B79

P52|PE3B_TX_DP[4]|PCIEX3|O;2B62

T52|PE3B_TX_DN[4]|PCIEX3|O;2B63

R51|PE3B_TX_DP[5]|PCIEX3|O;2B58

U51|PE3B_TX_DN[5]|PCIEX3|O;2B59

P50|PE3B_TX_DP[6]|PCIEX3|O;2B54

T50|PE3B_TX_DN[6]|PCIEX3|O;2B55

R49|PE3B_TX_DP[7]|PCIEX3|O;2B50

U49|PE3B_TX_DN[7]|PCIEX3|O;2B51

P48|PE3A_TX_DP[3]|PCIEX3|O;2B66

T48|PE3A_TX_DN[3]|PCIEX3|O;2B67

R47|PE3A_TX_DP[2]|PCIEX3|O;2B70

U47|PE3A_TX_DN[2]|PCIEX3|O;2B71

P46|PE3C_TX_DP[8]|PCIEX3|O;2B45

T46|PE3C_TX_DN[8]|PCIEX3|O;2B46

R45|PE3C_TX_DP[10]|PCIEX3|O;2B37

U45|PE3C_TX_DN[10]|PCIEX3|O;2B38

P44|PE3D_TX_DN[15]|PCIEX3|O;2B14

T44|PE3D_TX_DP[15]|PCIEX3|O;2B15

R43|DDR_SDA_C23|ODCMOS|I/O

U43|DDR_SCL_C23|ODCMOS|I/O

AA47|PE3C_TX_DP[9]|PCIEX3|O;2B41

AC47|PE3C_TX_DN[9]|PCIEX3|O;2B42

Y46|PE3C_TX_DP[11]|PCIEX3|O;2B33

AB46|PE3C_TX_DN[11]|PCIEX3|O;2B34

AA45|PE3D_TX_DP[12]|PCIEX3|O;2B27

AC45|PE3D_TX_DN[12]|PCIEX3|O;2B28

Y44|PE3D_TX_DP[13]|PCIEX3|O;2B23

AB44|PE3D_TX_DN[13]|PCIEX3|O;2B24

AA43|PE3D_TX_DN[14]|PCIEX3|O;2B19

AC43|PE3D_TX_DP[14]|PCIEX3|O;2B20

AT50|FRMAGENT|CMOS|I

AT48|BIST_ENABLE|CMOS|I

BA55|TEST4||I

BD50|ERROR_N[0]|ODCMOS|O

BJ53|PWRGOOD|CMOS|I

Update (added pins from the other 3/4 of the CPU):

AE27|DDR_RESET_C23_N|CMOS1.5v|O

D4|TEST3||O

F2|TEST2||O

CB18|DDR_RESET_C01_N|CMOS1.5v|O

CW17|DRAM_PWR_OK_C01|CMOS1.5v|I

DB4|TEST0||O

CW1|TEST1||O

full-size

https://www.dropbox.com/s/kjoo7grsaqb8azm/top01.png?dl=0

Last edited: