Got a tip for us?

Let us know

Become a MacRumors Supporter for $50/year with no ads, ability to filter front page stories, and private forums.

Which M.2 PCIe X16 adapter card?

- Thread starter MisterAndrew

- Start date

- Sort by reaction score

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

If your focus is MASSIVE data transfer speeds on a non-bootable data array... Equipped with 4 PCIe SSD's, the Amfeltec Squid delivers the fastest transfer rates on the MacPro.

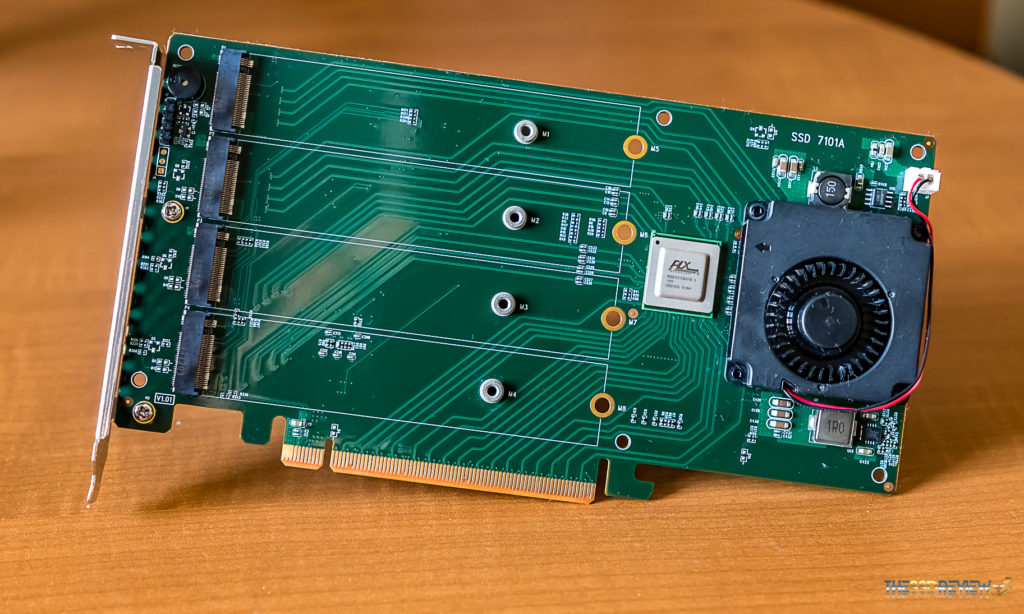

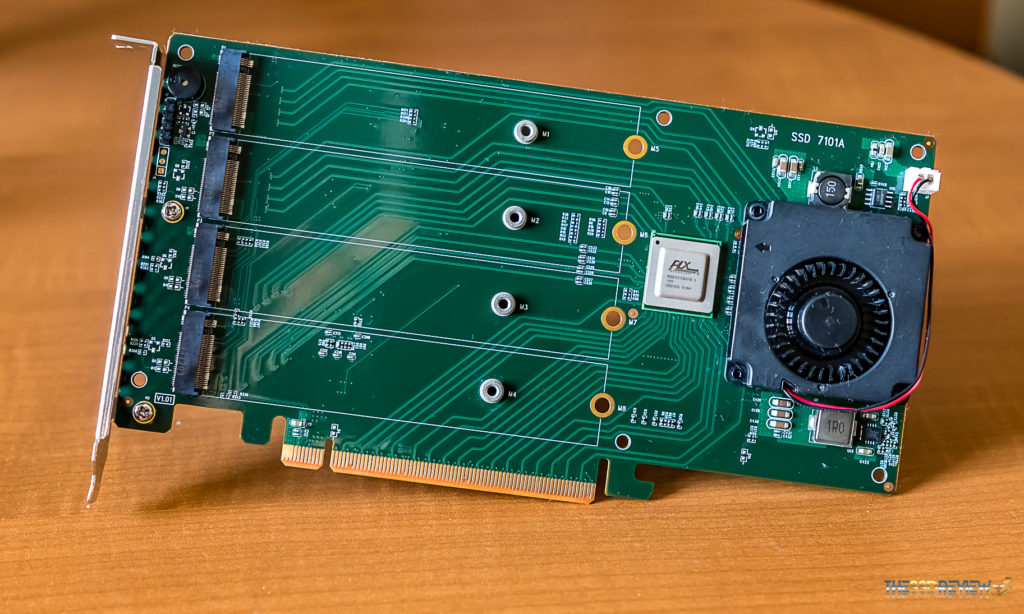

If your focus is the FASTEST Bootable PCIE SSD, the Highpoint 7101a, delivers some amazing numbers.

Even a single SM951 has 29% FASTER reads on the Highpoint 7101a. Write speed remains consistent.

If your focus is the FASTEST Bootable PCIE SSD, the Highpoint 7101a, delivers some amazing numbers.

Even a single SM951 has 29% FASTER reads on the Highpoint 7101a. Write speed remains consistent.

just for the sake of it, as soon as i will get the highpoint Ill try to see how it plays with a raid 0 of 8 drive 4 on the squid and 4 on the highpoint.If your focus is MASSIVE data transfer speeds on a non-bootable data array... Equipped with 4 PCIe SSD's, the Amfeltec Squid delivers the fastest transfer rates on the MacPro.

View attachment 768188

View attachment 768192

If your focus is the FASTEST Bootable PCIE SSD, the Highpoint 7101a, delivers some amazing numbers.

View attachment 768190

View attachment 768198

Even a single SM951 has 29% FASTER reads on the Highpoint 7101a. Write speed remains consistent.

View attachment 768199

View attachment 768200

my thoughts is that with my new 96 lane pcie expender I might be able to saturate the 16x link.

4 SM951's in the Highpoint 7101a dont scale as they do in the Amfeltec.

Running at the same speed as 3x SM951's

Running at the same speed as 3x SM951's

and by the way as i have 8 slot on the cyclone expender i will also try to go the extra mile by puting each sm951 in a passive adapter to see if the bigger pcie switch handle speed better.

it’s pretty ironic because back in 2009 they had nothing that could actually saturate a 16 x gen2 link in real life so it is quite amazing to see a 10 year old computer smoking a brand new 10k mac...

I have no doubt that someone at apple is having nightmares seing use doing what we do while in charge of the development of the 2019 macpro...

they better come up with somthing capable of 80 pcie gen 3 lane if they dont want to look dumb asking 10k

on the new 2019 modular macpro.

if you look at Puget system test, all video software are built for high end i9/amd threadripper and not anymore for workstation hardware.

If your focus is the FASTEST Bootable PCIE SSD, the Highpoint 7101a, delivers some amazing numbers.

View attachment 768190

View attachment 768198

Even a single SM951 has 29% FASTER reads on the Highpoint 7101a. Write speed remains consistent.

View attachment 768199

View attachment 768200[/QUOTE]

[doublepost=1530229059][/doublepost]yeah, i think that more of the available lane on the expender, the best it scale up...

but on the highpoint, the raid engine might become the botelneck while there is none on the amfeltec...

can you see if there is any ram on the highpoint?

maybe the amazing speed you saw with nvme is because there is no AHCI overhead in the raid controller...

it’s pretty ironic because back in 2009 they had nothing that could actually saturate a 16 x gen2 link in real life so it is quite amazing to see a 10 year old computer smoking a brand new 10k mac...

I have no doubt that someone at apple is having nightmares seing use doing what we do while in charge of the development of the 2019 macpro...

they better come up with somthing capable of 80 pcie gen 3 lane if they dont want to look dumb asking 10k

on the new 2019 modular macpro.

if you look at Puget system test, all video software are built for high end i9/amd threadripper and not anymore for workstation hardware.

If your focus is the FASTEST Bootable PCIE SSD, the Highpoint 7101a, delivers some amazing numbers.

View attachment 768190

View attachment 768198

Even a single SM951 has 29% FASTER reads on the Highpoint 7101a. Write speed remains consistent.

View attachment 768199

View attachment 768200[/QUOTE]

[doublepost=1530229059][/doublepost]yeah, i think that more of the available lane on the expender, the best it scale up...

but on the highpoint, the raid engine might become the botelneck while there is none on the amfeltec...

can you see if there is any ram on the highpoint?

maybe the amazing speed you saw with nvme is because there is no AHCI overhead in the raid controller...

4 SM951's in the Highpoint 7101a dont scale as they do in the Amfeltec.

View attachment 768206

Running at the same speed as 3x SM951's

View attachment 768207

[doublepost=1530229059][/doublepost]yeah, i think that more of the available lane on the expender, the best it scale up...and by the way as i have 8 slot on the cyclone expender i will also try to go the extra mile by puting each sm951 in a passive adapter to see if the bigger pcie switch handle speed better.

it’s pretty ironic because back in 2009 they had nothing that could actually saturate a 16 x gen2 link in real life so it is quite amazing to see a 10 year old computer smoking a brand new 10k mac...

I have no doubt that someone at apple is having nightmares seing use doing what we do while in charge of the development of the 2019 macpro...

they better come up with somthing capable of 80 pcie gen 3 lane if they dont want to look dumb asking 10k

on the new 2019 modular macpro.

if you look at Puget system test, all video software are built for high end i9/amd threadripper and not anymore for workstation hardware.

If your focus is the FASTEST Bootable PCIE SSD, the Highpoint 7101a, delivers some amazing numbers.

View attachment 768190

View attachment 768198

Even a single SM951 has 29% FASTER reads on the Highpoint 7101a. Write speed remains consistent.

View attachment 768199

View attachment 768200

but on the highpoint, the raid engine might become the botelneck while there is none on the amfeltec...

can you see if there is any ram on the highpoint?

maybe the amazing speed you saw with nvme is because there is no AHCI overhead in the raid controller...[/QUOTE]

No ram, just the 8747 PCIe bridge.

[doublepost=1530229059][/doublepost]yeah, i think that more of the available lane on the expender, the best it scale up...

but on the highpoint, the raid engine might become the botelneck while there is none on the amfeltec...

can you see if there is any ram on the highpoint?

maybe the amazing speed you saw with nvme is because there is no AHCI overhead in the raid controller...

No ram, just the 8747 PCIe bridge.

switch not a bridge

Thanks for clarifying my tech grammar.  I'll do my best to refrain from calling it a bridge.

I'll do my best to refrain from calling it a bridge.

PEX 8747

48-Lane, 5-Port PCI Express Gen 3 (8 GT/s) Switch, 27 x 27mm FCBGA

Technical Specification Document link

The ExpressLane™ PEX 8747 is a 48-lane, 5-port, PCIe Gen 3 switch device developed on 40nm technology. The PEX 8747 device offers Multi-Host PCI Express switching capability enabling users to connect a host to its respective endpoints via scalable, high bandwidth, non-blocking interconnection to a variety of graphics applications. The PEX 8747 is optimized to support high-resolution graphics while supporting peer-to-peer traffic and multicast for maximum performance. Included is PLX's proprietary visionPAK debug software, which allows, for example, internal receive-eye observation after equalization and access to the devices' internal debug registers thus enabling faster time to market.

PEX 8747

48-Lane, 5-Port PCI Express Gen 3 (8 GT/s) Switch, 27 x 27mm FCBGA

Technical Specification Document link

The ExpressLane™ PEX 8747 is a 48-lane, 5-port, PCIe Gen 3 switch device developed on 40nm technology. The PEX 8747 device offers Multi-Host PCI Express switching capability enabling users to connect a host to its respective endpoints via scalable, high bandwidth, non-blocking interconnection to a variety of graphics applications. The PEX 8747 is optimized to support high-resolution graphics while supporting peer-to-peer traffic and multicast for maximum performance. Included is PLX's proprietary visionPAK debug software, which allows, for example, internal receive-eye observation after equalization and access to the devices' internal debug registers thus enabling faster time to market.

With a NVMe boot EFI firmware modded following the step-by-step Google Doc I was asked to write..

It works great as a bootable m.2 adapter delivering PCIe 3.0 speeds on the cMP with a 970 pro, connected as a 8.0Gt/s device with 3000MB/sec reads, 2000 MB/sec writes.

Mojave public beta installed on the Highpoint 7101a without issue. TRIM is also enabled by default.

Apple SSD Controller:

Samsung SSD 970 PRO 512GB:

Capacity: 512.11 GB (512,110,190,592 bytes)

TRIM Support: Yes

Model: Samsung SSD 970 PRO 512GB

Revision: 1B2QEXP7

Serial Number: xxxxxxxxxxxxxxxxx

Link Width: x4

Link Speed: 8.0 GT/s

Detachable Drive: No

BSD Name: disk2

Partition Map Type: GPT (GUID Partition Table)

Removable Media: No

Volumes:

EFI:

Capacity: 209.7 MB (209,715,200 bytes)

File System: MS-DOS FAT32

BSD Name: disk2s1

Content: EFI

Volume UUID: 0E239BC6-F960-3107-89CF-1C97F78BB46B

disk2s2:

Capacity: 511.9 GB (511,900,434,432 bytes)

BSD Name: disk2s2

Content: Apple_APFS

AWESOME Google Doc!

I'm trying to make sense of this. Isn't the PCIe bus on the cMP is at best v2 (5GT/s)?

The PCIe switch on the Amfeltec sits between the SSDs on the card and the motherboard PCIe, right? So is the v3 performance reported the speed of the SSD to the card switch?

Maybe I could better wrap my head around this if you posted the output of the pcitree script from joevt (https://forums.macrumors.com/thread...4-ssds-5900-mb-s.1936311/page-9#post-25540266 post#223)?

Yes. The 8747 PLX provides a PCIe 3.0 bus for all 4 M.2 slots, allowing them to appear as 8.0 GT/S connections in hardware info.

Here is a snapshot of the output, showing the 8747 at +-07.0-[06-0b]

Details of the 8747 from lspci

Maximum capability

LnkCap: Port #0, Speed 8GT/s, Width x16, ASPM L1, Exit Latency L1 <4us

ClockPM- Surprise- LLActRep- BwNot- ASPMOptComp+

LnkCtl: ASPM Disabled; Disabled- CommClk-

ExtSynch- ClockPM- AutWidDis- BWInt- AutBWInt-

Current state

LnkSta: Speed 5GT/s (downgraded), Width x16 (ok)

TrErr- Train- SlotClk- DLActive- BWMgmt- ABWMgmt-

Here is a snapshot of the output, showing the 8747 at +-07.0-[06-0b]

Code:

-[0000:00]-+-00.0 Intel Corporation 5520/5500/X58 I/O Hub to ESI Port [8086:3405]

+-01.0-[01-04]----00.0-[02-04]--+-02.0-[03]--

| \-04.0-[04]--

+-03.0-[05]--+-00.0 Advanced Micro Devices, Inc. [AMD/ATI] Ellesmere [Radeon RX 470/480/570/580] [1002:67df]

| \-00.1 Advanced Micro Devices, Inc. [AMD/ATI] Ellesmere [Radeon RX 580] [1002:aaf0]

+-07.0-[06-0b]----00.0-[07-0b]--+-08.0-[08]--

| +-09.0-[09]--

| +-10.0-[0a]----00.0 Samsung Electronics Co Ltd Device [144d:a808]

| \-11.0-[0b]--Details of the 8747 from lspci

Maximum capability

LnkCap: Port #0, Speed 8GT/s, Width x16, ASPM L1, Exit Latency L1 <4us

ClockPM- Surprise- LLActRep- BwNot- ASPMOptComp+

LnkCtl: ASPM Disabled; Disabled- CommClk-

ExtSynch- ClockPM- AutWidDis- BWInt- AutBWInt-

Current state

LnkSta: Speed 5GT/s (downgraded), Width x16 (ok)

TrErr- Train- SlotClk- DLActive- BWMgmt- ABWMgmt-

Code:

06:00.0 PCI bridge: PLX Technology, Inc. PEX 8747 48-Lane, 5-Port PCI Express Gen 3 (8.0 GT/s) Switch (rev ca) (prog-if 00 [Normal decode])

Control: I/O+ Mem+ BusMaster+ SpecCycle- MemWINV- VGASnoop- ParErr- Stepping- SERR- FastB2B- DisINTx-

Status: Cap+ 66MHz- UDF- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- >SERR- <PERR- INTx-

Latency: 0, Cache Line Size: 256 bytes

Interrupt: pin A routed to IRQ 16

Region 0: Memory at 90600000 (32-bit, non-prefetchable)

Bus: primary=06, secondary=07, subordinate=0b, sec-latency=0

I/O behind bridge: None

Memory behind bridge: 90500000-905fffff [size=1M]

Prefetchable memory behind bridge: None

Secondary status: 66MHz- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- <SERR- <PERR-

BridgeCtl: Parity- SERR+ NoISA- VGA- VGA16- MAbort- >Reset- FastB2B-

PriDiscTmr- SecDiscTmr- DiscTmrStat- DiscTmrSERREn-

Capabilities: [40] Power Management version 3

Flags: PMEClk- DSI- D1- D2- AuxCurrent=0mA PME(D0+,D1-,D2-,D3hot+,D3cold+)

Status: D0 NoSoftRst+ PME-Enable- DSel=0 DScale=0 PME-

Capabilities: [48] MSI: Enable- Count=1/8 Maskable+ 64bit+

Address: 0000000000000000 Data: 0000

Masking: 00000000 Pending: 00000000

Capabilities: [68] Express (v2) Upstream Port, MSI 00

DevCap: MaxPayload 2048 bytes, PhantFunc 0

ExtTag- AttnBtn- AttnInd- PwrInd- RBE+ SlotPowerLimit 0.000W

DevCtl: CorrErr- NonFatalErr- FatalErr- UnsupReq-

RlxdOrd+ ExtTag- PhantFunc- AuxPwr- NoSnoop+

MaxPayload 128 bytes, MaxReadReq 128 bytes

DevSta: CorrErr+ NonFatalErr- FatalErr- UnsupReq+ AuxPwr- TransPend-

LnkCap: Port #0, Speed 8GT/s, Width x16, ASPM L1, Exit Latency L1 <4us

ClockPM- Surprise- LLActRep- BwNot- ASPMOptComp+

LnkCtl: ASPM Disabled; Disabled- CommClk-

ExtSynch- ClockPM- AutWidDis- BWInt- AutBWInt-

LnkSta: Speed 5GT/s (downgraded), Width x16 (ok)

TrErr- Train- SlotClk- DLActive- BWMgmt- ABWMgmt-

DevCap2: Completion Timeout: Not Supported, TimeoutDis-, LTR+, OBFF Via message

AtomicOpsCap: Routing+

DevCtl2: Completion Timeout: 50us to 50ms, TimeoutDis-, LTR-, OBFF Disabled

AtomicOpsCtl: EgressBlck-

LnkCtl2: Target Link Speed: 8GT/s, EnterCompliance- SpeedDis-

Transmit Margin: Normal Operating Range, EnterModifiedCompliance- ComplianceSOS-

Compliance De-emphasis: -6dB

LnkSta2: Current De-emphasis Level: -6dB, EqualizationComplete-, EqualizationPhase1-

EqualizationPhase2-, EqualizationPhase3-, LinkEqualizationRequest-

Capabilities: [a4] Subsystem: PLX Technology, Inc. PEX 8747 48-Lane, 5-Port PCI Express Gen 3 (8.0 GT/s) Switch

Capabilities: [100 v1] Device Serial Number ca-87-00-10-b5-df-0e-00

Capabilities: [fb4 v1] Advanced Error Reporting

UESta: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-

UEMsk: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-

UESvrt: DLP+ SDES+ TLP- FCP+ CmpltTO- CmpltAbrt- UnxCmplt- RxOF+ MalfTLP+ ECRC- UnsupReq- ACSViol-

CESta: RxErr- BadTLP- BadDLLP- Rollover- Timeout- AdvNonFatalErr+

CEMsk: RxErr- BadTLP- BadDLLP- Rollover- Timeout- AdvNonFatalErr+

AERCap: First Error Pointer: 1f, ECRCGenCap+ ECRCGenEn- ECRCChkCap+ ECRCChkEn-

MultHdrRecCap- MultHdrRecEn- TLPPfxPres- HdrLogCap-

HeaderLog: 00000000 00000000 00000000 00000000

Capabilities: [138 v1] Power Budgeting <?>

Capabilities: [10c v1] Secondary PCI Express <?>

Capabilities: [148 v1] Virtual Channel

Caps: LPEVC=0 RefClk=100ns PATEntryBits=8

Arb: Fixed- WRR32- WRR64- WRR128-

Ctrl: ArbSelect=Fixed

Status: InProgress-

VC0: Caps: PATOffset=03 MaxTimeSlots=1 RejSnoopTrans-

Arb: Fixed- WRR32- WRR64+ WRR128- TWRR128- WRR256-

Ctrl: Enable+ ID=0 ArbSelect=WRR64 TC/VC=ff

Status: NegoPending- InProgress-

Port Arbitration Table <?>

Capabilities: [e00 v1] Extended Capability ID 0x12

Capabilities: [b00 v1] Latency Tolerance Reporting

Max snoop latency: 0ns

Max no snoop latency: 0ns

Capabilities: [b70 v1] Vendor Specific Information: ID=0001 Rev=0 Len=010 <?>

07:08.0 PCI bridge: PLX Technology, Inc. PEX 8747 48-Lane, 5-Port PCI Express Gen 3 (8.0 GT/s) Switch (rev ca) (prog-if 00 [Normal decode])

Control: I/O+ Mem+ BusMaster+ SpecCycle- MemWINV- VGASnoop- ParErr- Stepping- SERR- FastB2B- DisINTx-

Status: Cap+ 66MHz- UDF- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- >SERR- <PERR- INTx-

Latency: 0, Cache Line Size: 256 bytes

Interrupt: pin A routed to IRQ 16

Bus: primary=07, secondary=08, subordinate=08, sec-latency=0

I/O behind bridge: None

Memory behind bridge: None

Prefetchable memory behind bridge: None

Secondary status: 66MHz- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- <SERR- <PERR-

BridgeCtl: Parity- SERR+ NoISA- VGA- VGA16- MAbort- >Reset- FastB2B-

PriDiscTmr- SecDiscTmr- DiscTmrStat- DiscTmrSERREn-

Capabilities: [40] Power Management version 3

Flags: PMEClk- DSI- D1- D2- AuxCurrent=0mA PME(D0+,D1-,D2-,D3hot+,D3cold+)

Status: D0 NoSoftRst+ PME-Enable- DSel=0 DScale=0 PME-

Capabilities: [48] MSI: Enable- Count=1/8 Maskable+ 64bit+

Address: 0000000000000000 Data: 0000

Masking: 00000000 Pending: 00000000

Capabilities: [68] Express (v2) Downstream Port (Slot+), MSI 00

DevCap: MaxPayload 2048 bytes, PhantFunc 0

ExtTag- RBE+

DevCtl: CorrErr- NonFatalErr- FatalErr- UnsupReq-

RlxdOrd+ ExtTag- PhantFunc- AuxPwr- NoSnoop+

MaxPayload 128 bytes, MaxReadReq 128 bytes

DevSta: CorrErr+ NonFatalErr- FatalErr- UnsupReq+ AuxPwr- TransPend-

LnkCap: Port #8, Speed 8GT/s, Width x8, ASPM L1, Exit Latency L1 <4us

ClockPM- Surprise+ LLActRep+ BwNot+ ASPMOptComp+

LnkCtl: ASPM Disabled; Disabled- CommClk-

ExtSynch- ClockPM- AutWidDis- BWInt- AutBWInt-

LnkSta: Speed 2.5GT/s (downgraded), Width x0 (downgraded)

TrErr- Train- SlotClk- DLActive- BWMgmt- ABWMgmt-

SltCap: AttnBtn- PwrCtrl- MRL- AttnInd- PwrInd- HotPlug- Surprise-

Slot #8, PowerLimit 25.000W; Interlock- NoCompl-

SltCtl: Enable: AttnBtn- PwrFlt- MRL- PresDet- CmdCplt- HPIrq- LinkChg-

Control: AttnInd Unknown, PwrInd Unknown, Power- Interlock-

SltSta: Status: AttnBtn- PowerFlt- MRL- CmdCplt- PresDet- Interlock-

Changed: MRL- PresDet- LinkState-

DevCap2: Completion Timeout: Not Supported, TimeoutDis-, LTR+, OBFF Via message ARIFwd+

AtomicOpsCap: Routing+

DevCtl2: Completion Timeout: 50us to 50ms, TimeoutDis-, LTR-, OBFF Disabled ARIFwd-

AtomicOpsCtl: EgressBlck-

LnkCtl2: Target Link Speed: 8GT/s, EnterCompliance- SpeedDis-, Selectable De-emphasis: -6dB

Transmit Margin: Normal Operating Range, EnterModifiedCompliance- ComplianceSOS-

Compliance De-emphasis: -6dB

LnkSta2: Current De-emphasis Level: -3.5dB, EqualizationComplete-, EqualizationPhase1-

EqualizationPhase2-, EqualizationPhase3-, LinkEqualizationRequest-

Capabilities: [a4] Subsystem: PLX Technology, Inc. PEX 8747 48-Lane, 5-Port PCI Express Gen 3 (8.0 GT/s) Switch

Capabilities: [100 v1] Device Serial Number ca-87-00-10-b5-df-0e-00

Capabilities: [fb4 v1] Advanced Error Reporting

UESta: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-

UEMsk: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-

UESvrt: DLP+ SDES+ TLP- FCP+ CmpltTO- CmpltAbrt- UnxCmplt- RxOF+ MalfTLP+ ECRC- UnsupReq- ACSViol-

CESta: RxErr- BadTLP- BadDLLP- Rollover- Timeout- AdvNonFatalErr+

CEMsk: RxErr- BadTLP- BadDLLP- Rollover- Timeout- AdvNonFatalErr+

AERCap: First Error Pointer: 1f, ECRCGenCap+ ECRCGenEn- ECRCChkCap+ ECRCChkEn-

MultHdrRecCap- MultHdrRecEn- TLPPfxPres- HdrLogCap-

HeaderLog: 00000000 00000000 00000000 00000000

Capabilities: [138 v1] Power Budgeting <?>

Capabilities: [10c v1] Secondary PCI Express <?>

Capabilities: [148 v1] Virtual Channel

Caps: LPEVC=0 RefClk=100ns PATEntryBits=8

Arb: Fixed- WRR32- WRR64- WRR128-

Ctrl: ArbSelect=Fixed

Status: InProgress-

VC0: Caps: PATOffset=03 MaxTimeSlots=1 RejSnoopTrans-

Arb: Fixed- WRR32- WRR64+ WRR128- TWRR128- WRR256-

Ctrl: Enable+ ID=0 ArbSelect=WRR64 TC/VC=ff

Status: NegoPending+ InProgress-

Port Arbitration Table <?>

Capabilities: [e00 v1] Extended Capability ID 0x12

Capabilities: [f24 v1] Access Control Services

ACSCap: SrcValid+ TransBlk+ ReqRedir+ CmpltRedir+ UpstreamFwd+ EgressCtrl+ DirectTrans+

ACSCtl: SrcValid- TransBlk- ReqRedir- CmpltRedir- UpstreamFwd- EgressCtrl- DirectTrans-

Capabilities: [b70 v1] Vendor Specific Information: ID=0001 Rev=0 Len=010 <?>

07:09.0 PCI bridge: PLX Technology, Inc. PEX 8747 48-Lane, 5-Port PCI Express Gen 3 (8.0 GT/s) Switch (rev ca) (prog-if 00 [Normal decode])

Control: I/O+ Mem+ BusMaster+ SpecCycle- MemWINV- VGASnoop- ParErr- Stepping- SERR- FastB2B- DisINTx-

Status: Cap+ 66MHz- UDF- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- >SERR- <PERR- INTx-

Latency: 0, Cache Line Size: 256 bytes

Interrupt: pin A routed to IRQ 17

Bus: primary=07, secondary=09, subordinate=09, sec-latency=0

I/O behind bridge: None

Memory behind bridge: None

Prefetchable memory behind bridge: None

Secondary status: 66MHz- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- <SERR- <PERR-

BridgeCtl: Parity- SERR+ NoISA- VGA- VGA16- MAbort- >Reset- FastB2B-

PriDiscTmr- SecDiscTmr- DiscTmrStat- DiscTmrSERREn-

Capabilities: [40] Power Management version 3

Flags: PMEClk- DSI- D1- D2- AuxCurrent=0mA PME(D0+,D1-,D2-,D3hot+,D3cold+)

Status: D0 NoSoftRst+ PME-Enable- DSel=0 DScale=0 PME-

Capabilities: [48] MSI: Enable- Count=1/8 Maskable+ 64bit+

Address: 0000000000000000 Data: 0000

Masking: 00000000 Pending: 00000000

Capabilities: [68] Express (v2) Downstream Port (Slot+), MSI 00

DevCap: MaxPayload 2048 bytes, PhantFunc 0

ExtTag- RBE+

DevCtl: CorrErr- NonFatalErr- FatalErr- UnsupReq-

RlxdOrd+ ExtTag- PhantFunc- AuxPwr- NoSnoop+

MaxPayload 128 bytes, MaxReadReq 128 bytes

DevSta: CorrErr+ NonFatalErr- FatalErr- UnsupReq+ AuxPwr- TransPend-

LnkCap: Port #9, Speed 8GT/s, Width x8, ASPM L1, Exit Latency L1 <4us

ClockPM- Surprise+ LLActRep+ BwNot+ ASPMOptComp+

LnkCtl: ASPM Disabled; Disabled- CommClk-

ExtSynch- ClockPM- AutWidDis- BWInt- AutBWInt-

LnkSta: Speed 2.5GT/s (downgraded), Width x0 (downgraded)

TrErr- Train- SlotClk- DLActive- BWMgmt- ABWMgmt-

SltCap: AttnBtn+ PwrCtrl+ MRL+ AttnInd+ PwrInd+ HotPlug+ Surprise-

Slot #9, PowerLimit 25.000W; Interlock- NoCompl-

SltCtl: Enable: AttnBtn- PwrFlt- MRL- PresDet- CmdCplt- HPIrq- LinkChg-

Control: AttnInd Off, PwrInd Off, Power+ Interlock-

SltSta: Status: AttnBtn- PowerFlt- MRL+ CmdCplt+ PresDet- Interlock-

Changed: MRL- PresDet- LinkState-

DevCap2: Completion Timeout: Not Supported, TimeoutDis-, LTR+, OBFF Via message ARIFwd+

AtomicOpsCap: Routing+

DevCtl2: Completion Timeout: 50us to 50ms, TimeoutDis-, LTR-, OBFF Disabled ARIFwd-

AtomicOpsCtl: EgressBlck-

LnkCtl2: Target Link Speed: 8GT/s, EnterCompliance- SpeedDis-, Selectable De-emphasis: -6dB

Transmit Margin: Normal Operating Range, EnterModifiedCompliance- ComplianceSOS-

Compliance De-emphasis: -6dB

LnkSta2: Current De-emphasis Level: -3.5dB, EqualizationComplete-, EqualizationPhase1-

EqualizationPhase2-, EqualizationPhase3-, LinkEqualizationRequest-

Capabilities: [a4] Subsystem: PLX Technology, Inc. PEX 8747 48-Lane, 5-Port PCI Express Gen 3 (8.0 GT/s) Switch

Capabilities: [100 v1] Device Serial Number ca-87-00-10-b5-df-0e-00

Capabilities: [fb4 v1] Advanced Error Reporting

UESta: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-

UEMsk: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-

UESvrt: DLP+ SDES+ TLP- FCP+ CmpltTO- CmpltAbrt- UnxCmplt- RxOF+ MalfTLP+ ECRC- UnsupReq- ACSViol-

CESta: RxErr- BadTLP- BadDLLP- Rollover- Timeout- AdvNonFatalErr+

CEMsk: RxErr- BadTLP- BadDLLP- Rollover- Timeout- AdvNonFatalErr+

AERCap: First Error Pointer: 1f, ECRCGenCap+ ECRCGenEn- ECRCChkCap+ ECRCChkEn-

MultHdrRecCap- MultHdrRecEn- TLPPfxPres- HdrLogCap-

HeaderLog: 00000000 00000000 00000000 00000000

Capabilities: [138 v1] Power Budgeting <?>

Capabilities: [10c v1] Secondary PCI Express <?>

Capabilities: [148 v1] Virtual Channel

Caps: LPEVC=0 RefClk=100ns PATEntryBits=8

Arb: Fixed- WRR32- WRR64- WRR128-

Ctrl: ArbSelect=Fixed

Status: InProgress-

VC0: Caps: PATOffset=03 MaxTimeSlots=1 RejSnoopTrans-

Arb: Fixed- WRR32- WRR64+ WRR128- TWRR128- WRR256-

Ctrl: Enable+ ID=0 ArbSelect=WRR64 TC/VC=ff

Status: NegoPending+ InProgress-

Port Arbitration Table <?>

Capabilities: [e00 v1] Extended Capability ID 0x12

Capabilities: [f24 v1] Access Control Services

ACSCap: SrcValid+ TransBlk+ ReqRedir+ CmpltRedir+ UpstreamFwd+ EgressCtrl+ DirectTrans+

ACSCtl: SrcValid- TransBlk- ReqRedir- CmpltRedir- UpstreamFwd- EgressCtrl- DirectTrans-

Capabilities: [b70 v1] Vendor Specific Information: ID=0001 Rev=0 Len=010 <?>

07:10.0 PCI bridge: PLX Technology, Inc. PEX 8747 48-Lane, 5-Port PCI Express Gen 3 (8.0 GT/s) Switch (rev ca) (prog-if 00 [Normal decode])

Control: I/O+ Mem+ BusMaster+ SpecCycle- MemWINV- VGASnoop- ParErr- Stepping- SERR- FastB2B- DisINTx-

Status: Cap+ 66MHz- UDF- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- >SERR- <PERR- INTx-

Latency: 0, Cache Line Size: 256 bytes

Interrupt: pin A routed to IRQ 16

Bus: primary=07, secondary=0a, subordinate=0a, sec-latency=0

I/O behind bridge: None

Memory behind bridge: 90500000-905fffff [size=1M]

Prefetchable memory behind bridge: None

Secondary status: 66MHz- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- <SERR- <PERR-

BridgeCtl: Parity- SERR+ NoISA- VGA- VGA16- MAbort- >Reset- FastB2B-

PriDiscTmr- SecDiscTmr- DiscTmrStat- DiscTmrSERREn-

Capabilities: [40] Power Management version 3

Flags: PMEClk- DSI- D1- D2- AuxCurrent=0mA PME(D0+,D1-,D2-,D3hot+,D3cold+)

Status: D0 NoSoftRst+ PME-Enable- DSel=0 DScale=0 PME-

Capabilities: [48] MSI: Enable- Count=1/8 Maskable+ 64bit+

Address: 0000000000000000 Data: 0000

Masking: 00000000 Pending: 00000000

Capabilities: [68] Express (v2) Downstream Port (Slot+), MSI 00

DevCap: MaxPayload 2048 bytes, PhantFunc 0

ExtTag- RBE+

DevCtl: CorrErr- NonFatalErr- FatalErr- UnsupReq-

RlxdOrd+ ExtTag- PhantFunc- AuxPwr- NoSnoop+

MaxPayload 128 bytes, MaxReadReq 128 bytes

DevSta: CorrErr+ NonFatalErr- FatalErr- UnsupReq+ AuxPwr- TransPend-

LnkCap: Port #16, Speed 8GT/s, Width x8, ASPM L1, Exit Latency L1 <4us

ClockPM- Surprise+ LLActRep+ BwNot+ ASPMOptComp+

LnkCtl: ASPM Disabled; Disabled- CommClk-

ExtSynch- ClockPM- AutWidDis- BWInt- AutBWInt-

LnkSta: Speed 8GT/s (ok), Width x4 (downgraded)

TrErr- Train- SlotClk- DLActive+ BWMgmt- ABWMgmt-

SltCap: AttnBtn- PwrCtrl- MRL- AttnInd- PwrInd- HotPlug- Surprise-

Slot #16, PowerLimit 25.000W; Interlock- NoCompl-

SltCtl: Enable: AttnBtn- PwrFlt- MRL- PresDet- CmdCplt- HPIrq- LinkChg-

Control: AttnInd Unknown, PwrInd Unknown, Power- Interlock-

SltSta: Status: AttnBtn- PowerFlt- MRL- CmdCplt- PresDet+ Interlock-

Changed: MRL- PresDet+ LinkState+

DevCap2: Completion Timeout: Not Supported, TimeoutDis-, LTR+, OBFF Via message ARIFwd+

AtomicOpsCap: Routing+

DevCtl2: Completion Timeout: 50us to 50ms, TimeoutDis-, LTR-, OBFF Disabled ARIFwd-

AtomicOpsCtl: EgressBlck-

LnkCtl2: Target Link Speed: 8GT/s, EnterCompliance- SpeedDis-, Selectable De-emphasis: -6dB

Transmit Margin: Normal Operating Range, EnterModifiedCompliance- ComplianceSOS-

Compliance De-emphasis: -6dB

LnkSta2: Current De-emphasis Level: -6dB, EqualizationComplete+, EqualizationPhase1+

EqualizationPhase2+, EqualizationPhase3+, LinkEqualizationRequest-

Capabilities: [a4] Subsystem: PLX Technology, Inc. PEX 8747 48-Lane, 5-Port PCI Express Gen 3 (8.0 GT/s) Switch

Capabilities: [100 v1] Device Serial Number ca-87-00-10-b5-df-0e-00

Capabilities: [fb4 v1] Advanced Error Reporting

UESta: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-

UEMsk: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-

UESvrt: DLP+ SDES+ TLP- FCP+ CmpltTO- CmpltAbrt- UnxCmplt- RxOF+ MalfTLP+ ECRC- UnsupReq- ACSViol-

CESta: RxErr- BadTLP- BadDLLP- Rollover- Timeout- AdvNonFatalErr+

CEMsk: RxErr- BadTLP- BadDLLP- Rollover- Timeout- AdvNonFatalErr+

AERCap: First Error Pointer: 1f, ECRCGenCap+ ECRCGenEn- ECRCChkCap+ ECRCChkEn-

MultHdrRecCap- MultHdrRecEn- TLPPfxPres- HdrLogCap-

HeaderLog: 00000000 00000000 00000000 00000000

Capabilities: [138 v1] Power Budgeting <?>

Capabilities: [10c v1] Secondary PCI Express <?>

Capabilities: [148 v1] Virtual Channel

Caps: LPEVC=0 RefClk=100ns PATEntryBits=8

Arb: Fixed- WRR32- WRR64- WRR128-

Ctrl: ArbSelect=Fixed

Status: InProgress-

VC0: Caps: PATOffset=03 MaxTimeSlots=1 RejSnoopTrans-

Arb: Fixed- WRR32- WRR64+ WRR128- TWRR128- WRR256-

Ctrl: Enable+ ID=0 ArbSelect=WRR64 TC/VC=ff

Status: NegoPending- InProgress-

Port Arbitration Table <?>

Capabilities: [e00 v1] Extended Capability ID 0x12

Capabilities: [f24 v1] Access Control Services

ACSCap: SrcValid+ TransBlk+ ReqRedir+ CmpltRedir+ UpstreamFwd+ EgressCtrl+ DirectTrans+

ACSCtl: SrcValid- TransBlk- ReqRedir- CmpltRedir- UpstreamFwd- EgressCtrl- DirectTrans-

Capabilities: [b70 v1] Vendor Specific Information: ID=0001 Rev=0 Len=010 <?>

07:11.0 PCI bridge: PLX Technology, Inc. PEX 8747 48-Lane, 5-Port PCI Express Gen 3 (8.0 GT/s) Switch (rev ca) (prog-if 00 [Normal decode])

Control: I/O+ Mem+ BusMaster+ SpecCycle- MemWINV- VGASnoop- ParErr- Stepping- SERR- FastB2B- DisINTx-

Status: Cap+ 66MHz- UDF- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- >SERR- <PERR- INTx-

Latency: 0, Cache Line Size: 256 bytes

Interrupt: pin A routed to IRQ 17

Bus: primary=07, secondary=0b, subordinate=0b, sec-latency=0

I/O behind bridge: None

Memory behind bridge: None

Prefetchable memory behind bridge: None

Secondary status: 66MHz- FastB2B- ParErr- DEVSEL=fast >TAbort- <TAbort- <MAbort- <SERR- <PERR-

BridgeCtl: Parity- SERR+ NoISA- VGA- VGA16- MAbort- >Reset- FastB2B-

PriDiscTmr- SecDiscTmr- DiscTmrStat- DiscTmrSERREn-

Capabilities: [40] Power Management version 3

Flags: PMEClk- DSI- D1- D2- AuxCurrent=0mA PME(D0+,D1-,D2-,D3hot+,D3cold+)

Status: D0 NoSoftRst+ PME-Enable- DSel=0 DScale=0 PME-

Capabilities: [48] MSI: Enable- Count=1/8 Maskable+ 64bit+

Address: 0000000000000000 Data: 0000

Masking: 00000000 Pending: 00000000

Capabilities: [68] Express (v2) Downstream Port (Slot+), MSI 00

DevCap: MaxPayload 2048 bytes, PhantFunc 0

ExtTag- RBE+

DevCtl: CorrErr- NonFatalErr- FatalErr- UnsupReq-

RlxdOrd+ ExtTag- PhantFunc- AuxPwr- NoSnoop+

MaxPayload 128 bytes, MaxReadReq 128 bytes

DevSta: CorrErr+ NonFatalErr- FatalErr- UnsupReq+ AuxPwr- TransPend-

LnkCap: Port #17, Speed 8GT/s, Width x8, ASPM L1, Exit Latency L1 <4us

ClockPM- Surprise+ LLActRep+ BwNot+ ASPMOptComp+

LnkCtl: ASPM Disabled; Disabled- CommClk-

ExtSynch- ClockPM- AutWidDis- BWInt- AutBWInt-

LnkSta: Speed 2.5GT/s (downgraded), Width x0 (downgraded)

TrErr- Train- SlotClk- DLActive- BWMgmt- ABWMgmt-

SltCap: AttnBtn- PwrCtrl- MRL- AttnInd- PwrInd- HotPlug- Surprise-

Slot #17, PowerLimit 25.000W; Interlock- NoCompl-

SltCtl: Enable: AttnBtn- PwrFlt- MRL- PresDet- CmdCplt- HPIrq- LinkChg-

Control: AttnInd Unknown, PwrInd Unknown, Power- Interlock-

SltSta: Status: AttnBtn- PowerFlt- MRL- CmdCplt- PresDet- Interlock-

Changed: MRL- PresDet- LinkState-

DevCap2: Completion Timeout: Not Supported, TimeoutDis-, LTR+, OBFF Via message ARIFwd+

AtomicOpsCap: Routing+

DevCtl2: Completion Timeout: 50us to 50ms, TimeoutDis-, LTR-, OBFF Disabled ARIFwd-

AtomicOpsCtl: EgressBlck-

LnkCtl2: Target Link Speed: 8GT/s, EnterCompliance- SpeedDis-, Selectable De-emphasis: -6dB

Transmit Margin: Normal Operating Range, EnterModifiedCompliance- ComplianceSOS-

Compliance De-emphasis: -6dB

LnkSta2: Current De-emphasis Level: -3.5dB, EqualizationComplete-, EqualizationPhase1-

EqualizationPhase2-, EqualizationPhase3-, LinkEqualizationRequest-

Capabilities: [a4] Subsystem: PLX Technology, Inc. PEX 8747 48-Lane, 5-Port PCI Express Gen 3 (8.0 GT/s) Switch

Capabilities: [100 v1] Device Serial Number ca-87-00-10-b5-df-0e-00

Capabilities: [fb4 v1] Advanced Error Reporting

UESta: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-

UEMsk: DLP- SDES- TLP- FCP- CmpltTO- CmpltAbrt- UnxCmplt- RxOF- MalfTLP- ECRC- UnsupReq- ACSViol-

UESvrt: DLP+ SDES+ TLP- FCP+ CmpltTO- CmpltAbrt- UnxCmplt- RxOF+ MalfTLP+ ECRC- UnsupReq- ACSViol-

CESta: RxErr- BadTLP- BadDLLP- Rollover- Timeout- AdvNonFatalErr+

CEMsk: RxErr- BadTLP- BadDLLP- Rollover- Timeout- AdvNonFatalErr+

AERCap: First Error Pointer: 1f, ECRCGenCap+ ECRCGenEn- ECRCChkCap+ ECRCChkEn-

MultHdrRecCap- MultHdrRecEn- TLPPfxPres- HdrLogCap-

HeaderLog: 00000000 00000000 00000000 00000000

Capabilities: [138 v1] Power Budgeting <?>

Capabilities: [10c v1] Secondary PCI Express <?>

Capabilities: [148 v1] Virtual Channel

Caps: LPEVC=0 RefClk=100ns PATEntryBits=8

Arb: Fixed- WRR32- WRR64- WRR128-

Ctrl: ArbSelect=Fixed

Status: InProgress-

VC0: Caps: PATOffset=03 MaxTimeSlots=1 RejSnoopTrans-

Arb: Fixed- WRR32- WRR64+ WRR128- TWRR128- WRR256-

Ctrl: Enable+ ID=0 ArbSelect=WRR64 TC/VC=ff

Status: NegoPending+ InProgress-

Port Arbitration Table <?>

Capabilities: [e00 v1] Extended Capability ID 0x12

Capabilities: [f24 v1] Access Control Services

ACSCap: SrcValid+ TransBlk+ ReqRedir+ CmpltRedir+ UpstreamFwd+ EgressCtrl+ DirectTrans+

ACSCtl: SrcValid- TransBlk- ReqRedir- CmpltRedir- UpstreamFwd- EgressCtrl- DirectTrans-

Capabilities: [b70 v1] Vendor Specific Information: ID=0001 Rev=0 Len=010 <?>

Last edited:

I've just got my own Highpoint 7101a .... and tested it with two Samsung 970 Evo 1TB SSDs:

The W/R speeds I'm getting are absolutely the same:

- one single SSD

- or two combined as a Raid 0

Write: 2500 MB/sec

Read: 2800 MB/sec

Is there anything I need to adjust to get better speeds?

My system: 5.1(flashed 4.1) running HighSierra 10.13.6

The W/R speeds I'm getting are absolutely the same:

- one single SSD

- or two combined as a Raid 0

Write: 2500 MB/sec

Read: 2800 MB/sec

Is there anything I need to adjust to get better speeds?

My system: 5.1(flashed 4.1) running HighSierra 10.13.6

I've just got my own Highpoint 7101a .... and tested it with two Samsung 970 Evo 1TB SSDs:

The W/R speeds I'm getting are absolutely the same:

- one single SSD

- or two combined as a Raid 0

Write: 2500 MB/sec

Read: 2800 MB/sec

Is there anything I need to adjust to get better speeds?

My system: 5.1(flashed 4.1) running HighSierra 10.13.6

Further upgrade the cMP's firmware to 138.0.0.0.0

this here, right?

Mojave Public Beta link:

You have to sign to the Apple Beta Program and download Mojave Public beta from https://beta.apple.com/sp/betaprogram/

You have to sign to the Apple Beta Program and download Mojave Public beta from https://beta.apple.com/sp/betaprogram/

this here, right?

Mojave Public Beta link:

You have to sign to the Apple Beta Program and download Mojave Public beta from https://beta.apple.com/sp/betaprogram/

Correct, just sign up, download the full installer, run it.

The installer will trigger the firmware update, but it won't install the OS, don't worry about it.

I've just got my own Highpoint 7101a .... and tested it with two Samsung 970 Evo 1TB SSDs:

The W/R speeds I'm getting are absolutely the same:

- one single SSD

- or two combined as a Raid 0

Write: 2500 MB/sec

Read: 2800 MB/sec

Is there anything I need to adjust to get better speeds?

My system: 5.1(flashed 4.1) running HighSierra 10.13.6

You probably have installed it into PCIe slots 1 or 2. They are running at PCIe v1 speed (2.5 GT/s) because of well known negotiation issues with PCIe v3 devices. Updating your firmware can fix this.

Yes, the SSD card is installed in slot 2. In the system overview it already appeared to be working with 8.0 GT/s and "x4" ... it was just not any faster as posted above...

but now:

I just did the firmware update. No installing of Mojave - still on HS 10.13.6

The 970-EVO-Raid 0 performs like this:

... awesome!

Thank you!!!

but now:

I just did the firmware update. No installing of Mojave - still on HS 10.13.6

The 970-EVO-Raid 0 performs like this:

... awesome!

Thank you!!!

Yes, the SSD card is installed in slot 2. In the system overview it already appeared to be working with 8.0 GT/s and "x4" ... it was just not any faster as posted above...

but now:

I just did the firmware update. No installing of Mojave - still on HS 10.13.6

The 970-EVO-Raid 0 performs like this:

View attachment 780649

... awesome!

Thank you!!!

The 8.0 GT/s is for the bridge chip on the card. It will work at 8.0 speed with the ssd cards, but the cMP PCIe is max 5.0.

You can get all the details on the speeds using pcitree, a command line program.

the fan noise

I think it's super annoying... no, it really is unbearable!! In the frist few days I was just amazed by the speed - now all I can think of this Highpoint card is: FAN NOISE!

... so I removed the aluminium cover and unplugged the fan. In order to avoid thermal overload I installed passive cooling elements:

It's running stable since a few days now -> much better

I think it's super annoying... no, it really is unbearable!! In the frist few days I was just amazed by the speed - now all I can think of this Highpoint card is: FAN NOISE!

... so I removed the aluminium cover and unplugged the fan. In order to avoid thermal overload I installed passive cooling elements:

It's running stable since a few days now -> much better

Last edited:

the fan noise

I think it's super annoying... no, it really is unbearable!! In the frist few days I was just amazed by the speed - now all I can think of this Highpoint card is: FAN NOISE!

... so I removed the aluminium cover and unplugged the fan. To order to avoid thermal overload I installed passive cooling elements:

View attachment 790048

It's running stable since a few days now -> much better

It looks like better to turn the cooler in 90 degree, so that the fins are in parallel of the airflow.

You probably have installed it into PCIe slots 1 or 2. They are running at PCIe v1 speed (2.5 GT/s) because of well known negotiation issues with PCIe v3 devices. Updating your firmware can fix this.

Just to make sure I understand what you're saying - are you referring to updating the bootrom firmware via the Mojave installer, or updating the firmware on the Highpoint card?

I updated the bootrom firmware via the Mojave installer: ... and boom! it's almost twice as fast

Just to make sure I understand what you're saying - are you referring to updating the bootrom firmware via the Mojave installer, or updating the firmware on the Highpoint card?

Update your cMP's firmware to 138.0.0.0.0 via the Mojave installer.

It looks like better to turn the cooler in 90 degree, so that the fins are in parallel of the airflow.

I'm not quite sure .. but you mean like this?

...ah, now I think I get it: you mean the expansion slot fan would blow some air through the cooler fins?

As the Sapphire Pulse Vega (2,5 slots wide) is partially blocking my 2nd slot: I have to use a riser cable to connect the Highpoint card. At the moment the card is still in an "experimental" location - just outside the tower housing - air flow is ok.

Last edited:

I updated the bootrom firmware via the Mojave installer: ... and boom! it's almost twice as fast

Update your cMP's firmware to 138.0.0.0.0 via the Mojave installer.

Fantastic - thank you both for the confirmation - just wanted to ensure I was understanding it as I was reading it.

Think this’ll work?

https://www.synology.com/en-global/products/M2D18

Controller is a Marvell 88SE9235 I believe.

https://www.synology.com/en-global/products/M2D18

Controller is a Marvell 88SE9235 I believe.

Last edited:

Register on MacRumors! This sidebar will go away, and you'll see fewer ads.