@nekton1 @Dayo thank you both so much for your input! the RAM issue was actually a problem for final install method (i.e., using dosdude1's patched installer)... the install would hang until i swapped out th ecurrent 64GB for 2GB RAM, and performance post-install was bad until implementing the boot-arg that @Dayo referenced. i may try again using OCLP, but with 2GB RAM installed and see if that changes things...

Got a tip for us?

Let us know

Become a MacRumors Supporter for $50/year with no ads, ability to filter front page stories, and private forums.

MP 1,1-5,1 OpenCore and the 2008 Mac Pro 3,1

- Thread starter amstel78

- WikiPost WikiPost

- Start date

- Sort by reaction score

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

- Status

- The first post of this thread is a WikiPost and can be edited by anyone with the appropiate permissions. Your edits will be public.

I'd be interested in testing if could get slot 4 to PCIe Gen 2.0 for my Titan-Ridge.I'm working on an EFI driver to fix the PCIe 2.0 link rate issue. It's gotten a little out of hand - I added the pci ids database from pciutils to recreate the output of pcitree.sh in EFI Shell. I'm currently working on adding code to search for hidden PCIe devices of Thunderbolt add-in cards. I would like the code to at least enable the USB of my GC-ALPINE RIDGE (to replace the startup.nsh method).

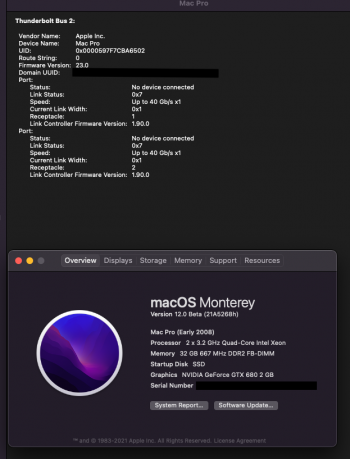

Just a heads-up. TB AIC runs fine too booted in Monterey beta 2 from NVMe SSD on HighPoint 7101. The first tests were booted from Sata SSD in standard Mac disk "slide" 3 booting Big Sur.It is showing 20 Gb/s on the connected TB port and 40 Gb/s on the open port.

I haven't clocked the true speed yet.

The boot NVMe Samsung SSD in the HighPoint 7101 uses the AIC's own PCIe Gen 3.0 chip so it gets much better speeds.

But this Titan-Ridge V2 TB card was a gift from a friend breaking an old Windows PC so no cost and a bit of fun/time hacking and coding to get it running.

Attachments

Last edited:

I'm working on an EFI driver to fix the PCIe 2.0 link rate issue. It's gotten a little out of hand - I added the pci ids database from pciutils to recreate the output of pcitree.sh in EFI Shell. I'm currently working on adding code to search for hidden PCIe devices of Thunderbolt add-in cards. I would like the code to at least enable the USB of my GC-ALPINE RIDGE (to replace the startup.nsh method).

I'd be interested in testing if could get slot 4 to PCIe Gen 2.0 for my Titan-Ridge.

Attached is a test driver.

Try the release version.

Put FixPCIeLinkRate.efi on a EFI partition somewhere (or any partition that is formatted as MS-DOS - FAT). The partition I use is the one that

fs0: would navigate me to in the EFI Shell.Run the EFI Shell (rEFInd or RefindPlus or OpenCore).

Change the mode to the widest/tallest mode (type

mode for a list of modes; I use mode 320 84 on my 2560x1600 display).Use the

cd command to go to the directory containing the efi driver file.Load the efi driver file like this:

load -nc FixPCIeLinkRate.efiYou'll see a list of your PCI devices with their max and current link rate/width. It will try to increase the link rate to the max for any device that appears to not by using their max.

The reason the load command is used is because I made it a EFI driver file instead of a EFI app - even though it doesn't add any protocols. Since it doesn't add any protocols, the -nc option is used to speed up the command (because no reconnecting of devices is required).

If you are satisfied with the result, you can move FixPCIeLinkRate.efi to the rEFInd or RefindPlus or OpenCore drivers folder or you can add a path to the driver in the Driver#### / DriverOrder boot variables (search for instructions elsewhere in the forum). I haven't tried these methods yet.

If there's an issue, you can try saving the output to a text file (you can only write files to FAT formatted partitions) like this:

load -nc FixPCIeLinkRate.efi > FixPCIeLinkRate.txtThe debug version is a lot more verbose - it log everything it does to the screen. If you have a problem with the release version, saving the output of the debug version to a text file may help to find where the problem might be in the code.

Here is the result for my MacPro3,1:

Code:

+[0000]

+-00:00.0 # g1x4 [8086:4003] [060000] Host bridge : Intel Corporation 5400 Chipset Memory Controller Hub

++00:01.0-[01-10] # g2x16 > g1x16 [8086:4021] [060400] PCI bridge (Normal decode) : Intel Corporation 5400 Chipset PCI Express Port 1

|`+01:00.0-[02-10] # g3x16 > g1x16 [10B5:8747] [060400] PCI bridge (Normal decode) : PLX Technology, Inc. PEX 8747 48-Lane, 5-Port PCI Express Gen 3 (8.0 GT/s) Switch

# g2x16 (updated parent)

# g3x16 > g2x16 (updated child)

| ++02:08.0-[03-08] # g3x8 > g3x4 [10B5:8747] [060400] PCI bridge (Normal decode) : PLX Technology, Inc. PEX 8747 48-Lane, 5-Port PCI Express Gen 3 (8.0 GT/s) Switch

| |`+03:00.0-[04-08] # g3x4 [8086:15EA] [060400] PCI bridge (Normal decode) : Intel Corporation JHL7540 Thunderbolt 3 Bridge [Titan Ridge 4C 2018]

| | ++04:00.0-[05] # g1x4 [8086:15EA] [060400] PCI bridge (Normal decode) : Intel Corporation JHL7540 Thunderbolt 3 Bridge [Titan Ridge 4C 2018]

| | |`-05:00.0 # g1x4 [8086:15EB] [088000] System peripheral : Intel Corporation JHL7540 Thunderbolt 3 NHI [Titan Ridge 4C 2018]

| | ++04:01.0-[06] # g1x4 [8086:15EA] [060400] PCI bridge (Normal decode) : Intel Corporation JHL7540 Thunderbolt 3 Bridge [Titan Ridge 4C 2018]

| | ++04:02.0-[07] # g1x4 [8086:15EA] [060400] PCI bridge (Normal decode) : Intel Corporation JHL7540 Thunderbolt 3 Bridge [Titan Ridge 4C 2018]

| | |`-07:00.0 # g1x4 [8086:15EC] [0C0330] USB controller (XHCI) : Intel Corporation JHL7540 Thunderbolt 3 USB Controller [Titan Ridge 4C 2018]

| | `+04:04.0-[08] # g1x4 [8086:15EA] [060400] PCI bridge (Normal decode) : Intel Corporation JHL7540 Thunderbolt 3 Bridge [Titan Ridge 4C 2018]

| ++02:09.0-[09-0E] # g3x8 > g3x4 [10B5:8747] [060400] PCI bridge (Normal decode) : PLX Technology, Inc. PEX 8747 48-Lane, 5-Port PCI Express Gen 3 (8.0 GT/s) Switch

| |`+09:00.0-[0A-0E] # g3x4 [8086:1136] [060400] PCI bridge (Normal decode) : Intel Corporation Thunderbolt 4 Bridge [Maple Ridge 4C 2020]

| | ++0A:00.0-[0B] # g1x4 [8086:1136] [060400] PCI bridge (Normal decode) : Intel Corporation Thunderbolt 4 Bridge [Maple Ridge 4C 2020]

| | |`-0B:00.0 # g1x4 [8086:1137] [0C0340] USB controller (USB4 Host Interface) : Intel Corporation Thunderbolt 4 NHI [Maple Ridge 4C 2020]

| | ++0A:01.0-[0C] # g1x4 [8086:1136] [060400] PCI bridge (Normal decode) : Intel Corporation Thunderbolt 4 Bridge [Maple Ridge 4C 2020]

| | ++0A:02.0-[0D] # g1x4 > g0x4 [8086:1136] [060400] PCI bridge (Normal decode) : Intel Corporation Thunderbolt 4 Bridge [Maple Ridge 4C 2020]

| | |`-0D:00.0 # g1x4 [8086:1138] [0C0330] USB controller (XHCI) : Intel Corporation Thunderbolt 4 USB Controller [Maple Ridge 4C 2020]

| | `+0A:03.0-[0E] # g1x4 [8086:1136] [060400] PCI bridge (Normal decode) : Intel Corporation Thunderbolt 4 Bridge [Maple Ridge 4C 2020]

| ++02:10.0-[0F] # g3x8 [10B5:8747] [060400] PCI bridge (Normal decode) : PLX Technology, Inc. PEX 8747 48-Lane, 5-Port PCI Express Gen 3 (8.0 GT/s) Switch

| |+-0F:00.0 # g3x16 > g3x8 [10DE:17C2] [030000] VGA compatible controller (VGA controller) : NVIDIA Corporation GM200 [GeForce GTX TITAN X]

| |`-0F:00.1 # g3x16 > g3x8 [10DE:0FB0] [040300] Audio device : NVIDIA Corporation GM200 High Definition Audio

| `+02:11.0-[10] # g3x8 > g3x4 [10B5:8747] [060400] PCI bridge (Normal decode) : PLX Technology, Inc. PEX 8747 48-Lane, 5-Port PCI Express Gen 3 (8.0 GT/s) Switch

| `+10:00.0-[00] # g3x4 [FFFF:FFFF] [060400] PCI bridge (Normal decode) : Illegal Vendor ID Device

| ++24:00.0-[00] # g1x4 [8086:1578] [060400] PCI bridge (Normal decode) : Intel Corporation DSL6540 Thunderbolt 3 Bridge [Alpine Ridge 4C 2015]

| |`-25:00.0 # g1x4 [8086:1577] [088000] System peripheral : Intel Corporation DSL6540 Thunderbolt 3 NHI [Alpine Ridge 4C 2015]

| ++24:01.0-[00] # g1x4 [8086:1578] [060400] PCI bridge (Normal decode) : Intel Corporation DSL6540 Thunderbolt 3 Bridge [Alpine Ridge 4C 2015]

| ++24:02.0-[00] # g1x4 [8086:1578] [060400] PCI bridge (Normal decode) : Intel Corporation DSL6540 Thunderbolt 3 Bridge [Alpine Ridge 4C 2015]

| |`-25:00.0 # g1x4 [8086:15B6] [0C0330] USB controller (XHCI) : Intel Corporation DSL6540 USB 3.1 Controller [Alpine Ridge]

| `+24:04.0-[00] # g1x4 [8086:1578] [060400] PCI bridge (Normal decode) : Intel Corporation DSL6540 Thunderbolt 3 Bridge [Alpine Ridge 4C 2015]

++00:05.0-[11] # g2x16 [8086:4025] [060400] PCI bridge (Normal decode) : Intel Corporation 5400 Chipset PCI Express Port 5

|+-11:00.0 # g2x16 [10DE:1180] [030000] VGA compatible controller (VGA controller) : NVIDIA Corporation GK104 [GeForce GTX 680]

|`-11:00.1 # g2x16 [10DE:0E0A] [040300] Audio device : NVIDIA Corporation GK104 HDMI Audio Controller

++00:09.0-[12-1A] # g2x4 > g1x4 [8086:4029] [060400] PCI bridge (Normal decode) : Intel Corporation 5400 Chipset PCI Express Port 9

|++12:00.0-[13-19] # g1x8 > g1x4 [8086:3500] [060400] PCI bridge (Normal decode) : Intel Corporation 6311ESB/6321ESB PCI Express Upstream Port

||++13:00.0-[14-17] # g1x4 [8086:3510] [060400] PCI bridge (Normal decode) : Intel Corporation 6311ESB/6321ESB PCI Express Downstream Port E1

|||`+14:00.0-[15-17] # g2x4 > g1x4 [12D8:2308] [060400] PCI bridge (Normal decode) : Pericom Semiconductor Device

||| ++15:01.0-[16] # g2x2 [12D8:2308] [060400] PCI bridge (Normal decode) : Pericom Semiconductor Device

||| |`-16:00.0 # g2x2 [1B21:1242] [0C0330] USB controller (XHCI) : ASMedia Technology Inc. ASM1142 USB 3.1 Host Controller

||| `+15:02.0-[17] # g2x2 [12D8:2308] [060400] PCI bridge (Normal decode) : Pericom Semiconductor Device

||| `-17:00.0 # g2x2 [1B21:0625] [010601] SATA controller (AHCI 1.0) : ASMedia Technology Inc. Device

||++13:01.0-[18] # g1x4 > g1x1 [8086:3514] [060400] PCI bridge (Normal decode) : Intel Corporation 6311ESB/6321ESB PCI Express Downstream Port E2

|||+-18:00.0 # g1x1 [125B:9100] [070002] Serial controller (16550) : Asix Electronics Corporation AX99100 PCIe to Multi I/O Controller

|||`-18:00.2 # g1x1 [125B:9100] [070002] Serial controller (16550) : Asix Electronics Corporation AX99100 PCIe to Multi I/O Controller

||`+13:02.0-[19] # g1x4 [8086:3518] [060400] PCI bridge (Normal decode) : Intel Corporation 6311ESB/6321ESB PCI Express Downstream Port E3

|| +-19:00.0 # g1x4 [8086:1096] [020000] Ethernet controller : Intel Corporation 80003ES2LAN Gigabit Ethernet Controller (Copper)

|| `-19:00.1 # g1x4 [8086:1096] [020000] Ethernet controller : Intel Corporation 80003ES2LAN Gigabit Ethernet Controller (Copper)

|`+12:00.3-[1A] # g1x8 > g1x4 [8086:350C] [060400] PCI bridge (Normal decode) : Intel Corporation 6311ESB/6321ESB PCI Express to PCI-X Bridge

+-00:0F.0 # g0x0 [8086:402F] [088000] System peripheral : Intel Corporation 5400 Chipset QuickData Technology Device

+-00:10.0 # [8086:4030] [060000] Host bridge : Intel Corporation 5400 Chipset FSB Registers

+-00:10.1 # [8086:4030] [060000] Host bridge : Intel Corporation 5400 Chipset FSB Registers

+-00:10.2 # [8086:4030] [060000] Host bridge : Intel Corporation 5400 Chipset FSB Registers

+-00:10.3 # [8086:4030] [060000] Host bridge : Intel Corporation 5400 Chipset FSB Registers

+-00:10.4 # [8086:4030] [060000] Host bridge : Intel Corporation 5400 Chipset FSB Registers

+-00:11.0 # [8086:4031] [060000] Host bridge : Intel Corporation 5400 Chipset CE/SF Registers

+-00:15.0 # [8086:4035] [060000] Host bridge : Intel Corporation 5400 Chipset FBD Registers

+-00:15.1 # [8086:4035] [060000] Host bridge : Intel Corporation 5400 Chipset FBD Registers

+-00:16.0 # [8086:4036] [060000] Host bridge : Intel Corporation 5400 Chipset FBD Registers

+-00:16.1 # [8086:4036] [060000] Host bridge : Intel Corporation 5400 Chipset FBD Registers

+-00:1B.0 # g0x0 [8086:269A] [040300] Audio device : Intel Corporation 631xESB/632xESB High Definition Audio Controller

++00:1C.0-[1B] # g1x1 > g1x0 [8086:2690] [060400] PCI bridge (Normal decode) : Intel Corporation 631xESB/632xESB/3100 Chipset PCI Express Root Port 1

++00:1C.1-[1C] # g1x1 > g1x0 [8086:2692] [060400] PCI bridge (Normal decode) : Intel Corporation 631xESB/632xESB/3100 Chipset PCI Express Root Port 2

++00:1C.2-[1D-1E] # g1x1 [8086:2694] [060400] PCI bridge (Normal decode) : Intel Corporation 631xESB/632xESB/3100 Chipset PCI Express Root Port 3

|`+1D:00.0-[1E] # g1x1 [104C:823E] [060400] PCI bridge (Normal decode) : Texas Instruments XIO2213A/B/XIO2221 PCI Express to PCI Bridge [Cheetah Express]

| `-1E:00.0 # [104C:823F] [0C0010] FireWire (IEEE 1394) (OHCI) : Texas Instruments XIO2213A/B/XIO2221 IEEE-1394b OHCI Controller [Cheetah Express]

++00:1C.3-[1F] # g1x1 [8086:2696] [060400] PCI bridge (Normal decode) : Intel Corporation 631xESB/632xESB/3100 Chipset PCI Express Root Port 4

|`-1F:00.0 # g1x1 [14E4:4328] [028000] Network controller : Broadcom Inc. and subsidiaries BCM4321 802.11a/b/g/n (AirPort Extreme)

+-00:1D.0 # [8086:2688] [0C0300] USB controller (UHCI) : Intel Corporation 631xESB/632xESB/3100 Chipset UHCI USB Controller #1

+-00:1D.1 # [8086:2689] [0C0300] USB controller (UHCI) : Intel Corporation 631xESB/632xESB/3100 Chipset UHCI USB Controller #2

+-00:1D.2 # [8086:268A] [0C0300] USB controller (UHCI) : Intel Corporation 631xESB/632xESB/3100 Chipset UHCI USB Controller #3

+-00:1D.3 # [8086:268B] [0C0300] USB controller (UHCI) : Intel Corporation 631xESB/632xESB/3100 Chipset UHCI USB Controller #4

+-00:1D.7 # [8086:268C] [0C0320] USB controller (EHCI) : Intel Corporation 631xESB/632xESB/3100 Chipset EHCI USB2 Controller

++00:1E.0-[20] # [8086:244E] [060401] PCI bridge (Subtractive decode) : Intel Corporation 82801 PCI Bridge

+-00:1F.0 # [8086:2670] [060100] ISA bridge : Intel Corporation 631xESB/632xESB/3100 Chipset LPC Interface Controller

+-00:1F.1 # [8086:269E] [01018F] IDE interface (PCI native mode controller, supports both channels switched to ISA compatibility mode, supports bus mastering) : Intel Corporation 631xESB/632xESB IDE Controller

+-00:1F.2 # [8086:2681] [010601] SATA controller (AHCI 1.0) : Intel Corporation 631xESB/632xESB SATA AHCI Controller

`-00:1F.3 # [8086:269B] [0C0500] SMBus : Intel Corporation 631xESB/632xESB/3100 Chipset SMBus Controller

load: Image fs0:\drivers\FixPCIeLinkRate.efi loaded at 79B7D000 - SuccessThere's a few things to notice here:

The driver is large (1.9 MB) because it includes the pci ids database (converted to C code).

The output is not as pretty as my pcitree.sh script. I had to use ASCII characters (+ + | ` -) because even though EFI supports unicode (UCS-2 which is similar to UTF-16) characters (┬ ├ │ └ ─), the EFI Shell's font doesn't include non-ASCII characters? Does the Shell included with Open Core have the same issue?

My Mac Pro has a Netstor NA255A connected to slot 2. The highest link rate shared by the parent root port (00:01.0 capable of gen 3) and the child device (01:00.0 capable of gen 2) is gen 2 which is greater than the current link rate of gen 1 so the code tries to set the link rate to gen 2. When link training completes, it shows the updated link rates of the parent and child. If the link rate didn't update then there may be an issue.

The Netstor contains an unmodified Nvidia Titan X (Maxwell) - I would like to make a driver that can make this work as a boot screen on MacPro3,1 even without RefindPlus or OpenCore.

The Netstor contains unmodified GC-TITAN RIDGE, ThunderboltEX 4, and GC-ALPINE RIDGE. The first two allow USB and Displayport Alt Mode. The GC-ALPINE RIDGE is hidden at boot - the parent device (02:11.0) has a secondary/subordinate bus (-[10]) that points to the GC-ALPINE RIDGE but the vendor and product ID are FFFF:FFFF so EFI doesn't enumerate the device. FixPCIeLinkRate.efi can detect it because only the vendor and product ID are FFFF. FixPCIeLinkRate.efi can read the other PCIe registers - if they are not FFFF then there's a device there (10:00.0-[00]). The upstream bridge of the GC-TITAN RIDGE has no secondary bus or subordinate bus (they are set to [00]). FixPCIeLinkRate.efi assigns buses in that case to search for children. The way the renumbering works is: it finds the largest range of unused buses (in my case, it's 21-FF since the last bus assigned is 20 for the non-existant children of 00:1E.0) and then renumbers the entire chain using those bus numbers:

Code:

┬[0000] ┬[0000]

└┬00:01.0-[01-10] └┬00:01.0-[21-FF]

└┬01:00.0-[02-10] └┬21:00.0-[22-FF]

└┬02:11.0-[10] └┬22:11.0-[23-FF]

└┬10:00.0-[00] └┬23:00.0-[24-FF]Now it can detect the children on bus 24. After detecting the children, it restores the original bus numbers because there are other buses in this chain and EFI devices already using those buses. It might be bad if one of those devices contained the display or EFI partition - I should probably add a nvram variable to disable the search for children. To make the renumbering permanent, a method to destruct those devices and reenumerate would be required and I don't think that's doable in MacPro3,1 EFI? The renumbering of buses may be easier if the Thunderbolt add-in card is in a root port - but the same problem of other devices existing in the chain still remains for the GC-TITAN RIDGE and ThunderboltEX 4 case. The process of detecting children continues for each new bridge that doesn't have a secondary/subordinate bus assigned - so the next level of children will appear on bus 25. If they had children then they would all appear as bus 26. Of course, if they were properly enumerated, each would have a different bus number (i.e. only one child would have bus 25). Anyway, FixPCIeLinkRate.efi only shows the original bus numbers in the final output (except for the detected children at bus 24 and up).

I am currently adding code to unhide the GC-ALPINE RIDGE. macOS will then be able to properly enumerate it and its immediate children (the XHCI and NHI), including the USB XHCI so I can connect USB devices to it. After that, I'll see if there's a way to make the Thunderbolt cards enable downstream Thunderbolt devices. Then the child scan should be able to find those PCIe devices. Currently, I have all the Thunderbolt code from edk2-platforms compiling but it's not all usable since it's dependant on certain motherboards (PCH registers, GPIO hardware, NVRAM variables, ACPI, etc.) and some of that code is not meant for the dxe stage. Adding code to earlier EFI stages (pei, etc.) requires firmware modification? For hackintoshes, people are adding Mac EFI Thunderbolt drivers to PC BIOS.... I won't be trying that.

Udate: FixPCIeLinkRate.efi source code on GitHub

Attachments

Last edited:

I don't use OpenCore. Is there an OpenShell item in OpenCore? Press the space-bar in the OpenCore menu to see it?Sorry but I don't underand what you mean by this line. I don't use rEFIND or RefindPlus and don't see where to run EFI shell in OpenCore (Configurator?)

"Run the EFI Shell (rEFInd or RefindPlus or OpenCore)."

Maybe check the documentation.

https://dortania.github.io/OpenCore-Install-Guide/installer-guide/opencore-efi.html

https://dortania.github.io/OpenCore-Install-Guide/installation/installation-process.html

https://dortania.github.io/OpenCore-Post-Install/multiboot/bootstrap.html

https://dortania.github.io/OpenCore-Multiboot/oc/win.html

https://dortania.github.io/OpenCore-Multiboot/oc/linux.html

https://dortania.github.io/docs/release/Configuration.html

Is OpenShell updated to work on old EFI 1.1 Macs? I don't think it worked on my MacPro3,1 when I last tried it. Therefore you may want to use the EFI 1.1 compatible shell:

EFI 1.1 compatible shell: https://github.com/tianocore/edk2/tree/UDK2018/EdkShellBinPkg/FullShell/X64

UEFI 2.x compatible shell: https://github.com/tianocore/edk2/tree/UDK2018/ShellBinPkg/UefiShell/X64

After you verify it works using the EFI Shell, you can try setting it up using the Driver#### option. This has the benefit of loading the driver even if you don't use OpenCore or RefindPlus or rEFInd.

https://forums.macrumors.com/threads/mac-pro-3-1-nvme-support-upgrade-guide-questions.2194878/

If there's a problem, it can be undone by zapping the PRAM but then you'll need to redo boot-args, default boot option, etc.

You have a PCIe gen 3 device in slot two that was running at gen 1 speed before? Now it should be working at gen 2 speed. If it's a Thunderbolt add-in card, then you should be able to get 1500 MB/s instead of just 800 MB/s.Hi joevt. Thanks for your work. I took a leap of faith and put your .efi file in the OC EFI Drivers folder and rebooted—pleased to say no adverse effects but I have no idea how to test for positive effects!

Any suggestions?

lspci -vvv from pciutils should be able to show the link rate.@joevt: Great job, this efi driver works like a charm. Thank you soo much.

Now both graphics card (slot 1) and NVMe (slot 2) show up in system report -> PCI with 5GT/s on my MacPro3,1 and the NVMe speed is around 1400 MB/s without the launch daemon and SIP now fully enabled again.

Also CL!ng shows transfer rates of about 4200 MB/s for the graphic card now, where it was around 2500 MB/s before.

I can also confirm that OpenShell.efi that comes with OpenCore 0.7.0 works well on my MacPro3.1.

Printout of the driver using the load -nc command looked like expected.

Now both graphics card (slot 1) and NVMe (slot 2) show up in system report -> PCI with 5GT/s on my MacPro3,1 and the NVMe speed is around 1400 MB/s without the launch daemon and SIP now fully enabled again.

Also CL!ng shows transfer rates of about 4200 MB/s for the graphic card now, where it was around 2500 MB/s before.

I can also confirm that OpenShell.efi that comes with OpenCore 0.7.0 works well on my MacPro3.1.

Printout of the driver using the load -nc command looked like expected.

Maybe OpenShell didn't work for me because I was trying it from rEFInd or RefindPlus. I'll have to retest this when I get into OpenCore again.@joevt: Great job, this efi driver works like a charm. Thank you soo much.

Now both graphics card (slot 1) and NVMe (slot 2) show up in system report -> PCI with 5GT/s on my MacPro3,1 and the NVMe speed is around 1400 MB/s without the launch daemon and SIP now fully enabled again.

Also CL!ng shows transfer rates of about 4200 MB/s for the graphic card now, where it was around 2500 MB/s before.

I can also confirm that OpenShell.efi that comes with OpenCore 0.7.0 works well on my MacPro3.1.

Printout of the driver using the load -nc command looked like expected.

Your GPU is the RX480? I think I remember that PCIe link retraining doesn't work with some GPUs - maybe Nvidia. Instead, those GPUs will use gen 1 link rate when idle and gen 2 when doing 3D work.

You've seen the output in OpenShell using the load -nc command. Have you tried to make OpenCore load the driver automatically from its driver folder? Does the output show in that case?

It should be safe to load the driver multiple times in the Shell or otherwise. The second time it runs, it will not change anything because the link rate was fixed during the first execution.

@joevt: The RX480 used to be below 3000 MB/s in CL!ING irrespective of what I did.

Now I am consistently above 4500 MB/s for Device to Host and 5800 MB/s for Host to Device.

If it is important for your development I can disable the driver and reconfirm numbers without.

I did execute the load -nc command twice and no issues. And as you said it did not change anything the second time.

Meanwhile I have placed your driver into the EFI/OC/Drivers and added it to the config.plist. I don‘t see any text on the screen before the boot picker and afterwards just the apple progress bar.

I have not tried verbose boot.

Update: Just confirmed transfer rates in CL!ng without the driver being consistently around 3000 MB/s.

I also just remembered that I don't have any screen before the boot picker since RX480 is not supported by Mac Pro firmware, so I would not see any text from the driver. I do have a HD7950 with MacROM lying around, if further tests are needed.

Now I am consistently above 4500 MB/s for Device to Host and 5800 MB/s for Host to Device.

If it is important for your development I can disable the driver and reconfirm numbers without.

I did execute the load -nc command twice and no issues. And as you said it did not change anything the second time.

Meanwhile I have placed your driver into the EFI/OC/Drivers and added it to the config.plist. I don‘t see any text on the screen before the boot picker and afterwards just the apple progress bar.

I have not tried verbose boot.

Update: Just confirmed transfer rates in CL!ng without the driver being consistently around 3000 MB/s.

I also just remembered that I don't have any screen before the boot picker since RX480 is not supported by Mac Pro firmware, so I would not see any text from the driver. I do have a HD7950 with MacROM lying around, if further tests are needed.

Last edited:

I don't think further tests are needed with your setup. I would like to see the output from theUpdate: Just confirmed transfer rates in CL!ng without the driver being consistently around 3000 MB/s.

I also just remembered that I don't have any screen before the boot picker since RX480 is not supported by Mac Pro firmware, so I would not see any text from the driver. I do have a HD7950 with MacROM lying around, if further tests are needed.

load -nc FixPCIeLinkRate.efi > FixPCIeLinkRate.txt command since you have more than one device affected (the output needs to be captured without OpenCore loading the driver beforehand.Hi Inspector42. Why/what lines did you add to config.plist? I don't think I read anything from joevt about doing this but maybe I missed it.Meanwhile I have placed your driver into the EFI/OC/Drivers and added it to the config.plist.

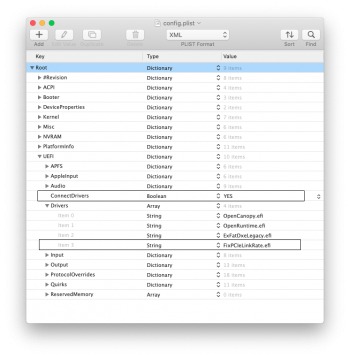

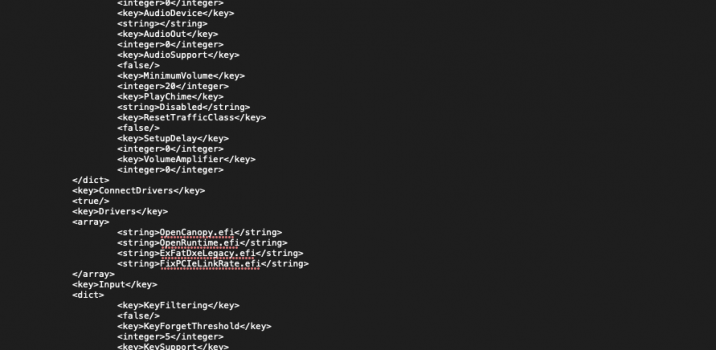

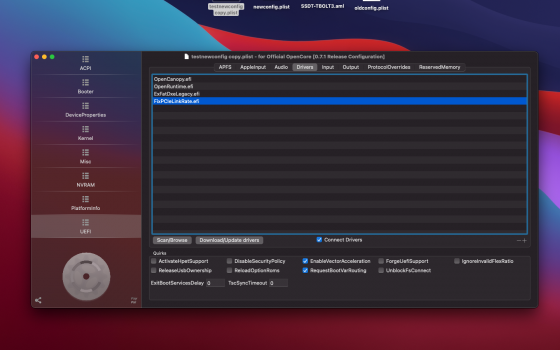

I did not mention it. Instructions for adding a driver using OpenCore or rEFInd can be found in their documentation.Hi Inspector42. Why/what lines did you add to config.plist? I don't think I read anything from joevt about doing this but maybe I missed it.

For rEFInd, you put the driver in a specific folder. The conf file has an option (

scan_driver_dirs) to add to the list of folders that are scanned for drivers but you can just use the default location drivers_x64https://www.rodsbooks.com/refind/drivers.html

https://www.rodsbooks.com/refind/configfile.html

For OpenCore, you need place the driver in the Drivers folder and list the driver name in the config file (

Drivers) and enable them ( ConnectDrivers)https://dortania.github.io/docs/latest/Configuration.html

I have attached a screenshot of my config and marked the relevant entries.

If the driver is not listed in the "Driver" section, OpenCore will not load it. No need to specify the path as long as the drivers reside in the /EFI/OC/Drivers folder.

If the driver is not listed in the "Driver" section, OpenCore will not load it. No need to specify the path as long as the drivers reside in the /EFI/OC/Drivers folder.

Attachments

Last edited:

What's the current status on Big Sur and the 3,1? There's a lot of information in this thread, though I'm not sure what would be relevant to me.

I have a 3,1; HD5770, 2.8QC x2, 500GB SSD + 500GB HDD both sata, 28GB 667MHz and 2x SuperDrive. Now I know that I'll at least have to find myself a GTX680 or different Metal based GPU - and that is kind-of where the painpoint lies. Those devices are about €100 here, which may or may not be worth it, depending on the stability of the system. I'm also aware of the BT card that needs replacing if I want to continue using that...

For what I've read here, there will be some AppleHDA patching necessary at least for audio? I'm planning on using optical out. And there may be issues with the onboard USB controller? And is the stability okay after all that patching, or is it like the good ole days of Hackintosh: First read every changelog after an update and wait for someone with more cojones than you to try it out?

I have a 3,1; HD5770, 2.8QC x2, 500GB SSD + 500GB HDD both sata, 28GB 667MHz and 2x SuperDrive. Now I know that I'll at least have to find myself a GTX680 or different Metal based GPU - and that is kind-of where the painpoint lies. Those devices are about €100 here, which may or may not be worth it, depending on the stability of the system. I'm also aware of the BT card that needs replacing if I want to continue using that...

For what I've read here, there will be some AppleHDA patching necessary at least for audio? I'm planning on using optical out. And there may be issues with the onboard USB controller? And is the stability okay after all that patching, or is it like the good ole days of Hackintosh: First read every changelog after an update and wait for someone with more cojones than you to try it out?

The only thing that you can’t get around is a metal capable graphic card. I had it work with a HD7950, which can be flashed for Mac boot screen and should be available for a lot less than €100 with a little patience and luck.

Everything else can be found here:

Audio and USB work without hardware changes. For BT you could use a usb-dongle or a fenvi PCIe card (https://m.de.aliexpress.com/item/10...90990240-00440-UneMJZVf&device=m&gclsrc=aw.ds)

Ammendment: BigSur beyond 11.2.3 has a race condition that occasionally prevents boot and can cause corruption of content on connected drives. Culprit has not been found yet. There is a separate thread in this forum - search for “latebloom”

Everything else can be found here:

Audio and USB work without hardware changes. For BT you could use a usb-dongle or a fenvi PCIe card (https://m.de.aliexpress.com/item/10...90990240-00440-UneMJZVf&device=m&gclsrc=aw.ds)

Ammendment: BigSur beyond 11.2.3 has a race condition that occasionally prevents boot and can cause corruption of content on connected drives. Culprit has not been found yet. There is a separate thread in this forum - search for “latebloom”

Last edited:

Register on MacRumors! This sidebar will go away, and you'll see fewer ads.